Featuring LeCroy's

# **SDA-PCIE-G2**

# New Compliance Framework FOR PCI Express Gen1(v1.0a, v1.1) and Gen2 (v0.5)

**Operator's Manual**

October 2005

### **LeCroy Corporation**

700 Chestnut Ridge Road Chestnut Ridge, NY 10977–6499 Tel: (845) 578 6020, Fax: (845) 578 5985

Internet: www.lecroy.com

© 2005 by LeCroy Corporation. All rights reserved.

LeCroy, ActiveDSO, ProBus, SMART Trigger, JitterTrack, WavePro, WaveMaster, WaveSurfer, and Waverunner are registered trademarks of LeCroy Corporation. Other product or brand names are trademarks or requested trademarks of their respective holders. Information in this publication supersedes all earlier versions. Specifications subject to change without notice.

PCIE-G2-OM-E Rev A 913660 Rev A

| INTRODUCTION TO SDA-PCIE-G2                                 | 3    |

|-------------------------------------------------------------|------|

| Required equipment                                          |      |

| PCI Express Compliance Test Fixtures                        | 3    |

| SOFTWARE INSTALLATION AND SYSTEM CONFIGURATION              | 7    |

| What Is X-Replay?                                           |      |

| Option Key Installation                                     |      |

| CD-ROM Installation                                         |      |

| Typical (Recommended) Configuration                         |      |

| Remote (Networked) Configuration                            |      |

|                                                             |      |

| INTRODUCTION TO PCI-EXPRESS                                 |      |

| PCI Express Device Development Process                      |      |

| PCI Express Device Development Process and Compliance Tests | 12   |

| PCI EXPRESS MEASUREMENT THEORY                              | . 14 |

| Eye Pattern and Jitter Measurements                         |      |

| Version 1.0a Measurements                                   | 14   |

| Version 1.1 Measurements                                    |      |

|                                                             |      |

| PREPARING TO MAKE PCI EXPRESS MEASUREMENTS                  |      |

| Channel Deskew (SMA Cables)                                 |      |

| Differential Probe Calibration                              |      |

| For SDA 6000A                                               | 19   |

| COMPLIANCE TEST MODE                                        | . 20 |

| Performing a Compliance Test – PCIe Signal Quality          |      |

| Performing a PCI Express Simple Measurement                 |      |

| Voltage measurements                                        |      |

| Timing measurements                                         |      |

| SSC measurements                                            | 25   |

| CHECKLIST TEST MODE OF OPERATION                            | 27   |

| Use of Configuration Variables in Test Sequences            |      |

| Menu Structure                                              |      |

| File                                                        |      |

| Edit                                                        |      |

| Sequence                                                    |      |

| Result Log                                                  |      |

| Report                                                      |      |

| Options                                                     |      |

| Devices                                                     |      |

| View                                                        | 31   |

| Help                                                        |      |

| Running PCI Express Tests                                   | 31   |

| Export to *.XML file – Database Access                      |      |

| TEST SEQUENCE REFERENCE                                     |      |

| General Information (Batch/Device Info)                     |      |

| PCI Express Tests                                           |      |

| GENERAL TESTS                                               |      |

| Clock Accuracy - Test 1.1                                   |      |

| SSC Tx Params: Test 1.2                                     |      |

| SSC Rate Tracking: Test 1.3                                 |      |

| TRANSMITTER TESTS<br>Tests 1.4 and 1.5: Compliance          |      |

| Test 1.6: DC Common Mode                                    |      |

|                                                             | +    |

# PCIE-G2 Software Option

| Test 1.7: Electrical Idle                                               | 35 |

|-------------------------------------------------------------------------|----|

| Test 1.8: RX Detect Voltage                                             | 35 |

| Test 1.9: RX Detect Hi-Z                                                | 35 |

| Test 1.10: RX Detect Low-Z                                              | 35 |

| Test 1.11: Lane Skew                                                    | 36 |

| Test 1.12: Rise/Fall                                                    | 36 |

| Test 1.15: Idle Voltage                                                 | 36 |

| Test 1.16: Idle Transition                                              | 36 |

| Test 1.17: RX Detect Sequence                                           | 37 |

| Test 1.18: Beacon or Wake#                                              | 37 |

| Test 1.19: Electrical Idle Exit                                         | 37 |

| Test 1.29: Beacon Propagation                                           | 37 |

| Test 1.30: Wakeup Propagation                                           | 37 |

| Receiver Tests                                                          | 37 |

| Test 1.14: DC Common Mode                                               | 37 |

| Test 1.20: DC Impedance                                                 | 38 |

| Test 1.21: Receiver Sensitivity                                         | 38 |

| Test 1.22: Unexpected Idle                                              | 38 |

| Test 1.23: Skew                                                         | 38 |

| SYSTEM BOARD TESTS                                                      |    |

| Test 1.5: Signal Quality (Compliance)                                   |    |

| Test 1.21: Receiver Sensitivity                                         |    |

| Test 1.24: V <sub>AUX</sub> Power (wake)                                |    |

| Test 1.25: V <sub>AUX</sub> Power (non-wake)                            | 39 |

| Test 1.26: Platform Power                                               |    |

| Test 1.5: Signal Quality (Compliance)                                   |    |

| Test 1.21: Receiver Sensitivity                                         |    |

| Test 1.27: Link Training                                                |    |

| Test 1.28: Down-Shifting                                                |    |

| Test 1.31: Add-In Power                                                 |    |

| REFCLK Tests (PCIe1.1 only)                                             |    |

| Changes from Version 1.0a                                               |    |

| Single-Ended Tests                                                      |    |

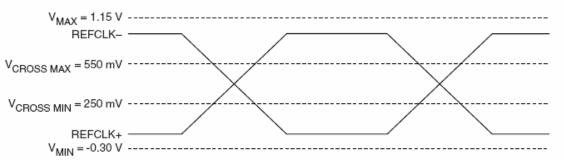

| Input Voltage                                                           |    |

| Crossing Voltage                                                        |    |

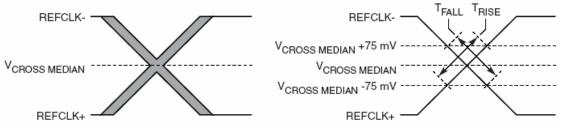

| Rise Fall Matching                                                      |    |

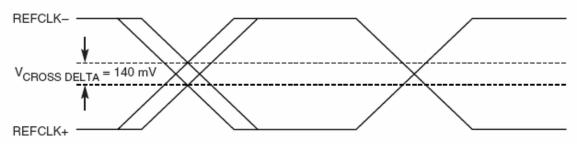

| Differential Tests                                                      |    |

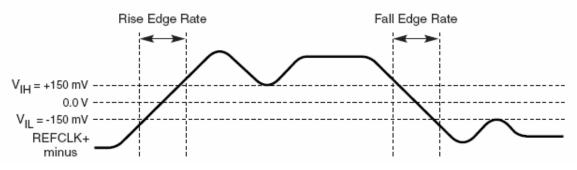

| Edge Rate                                                               |    |

| Differential Voltage                                                    |    |

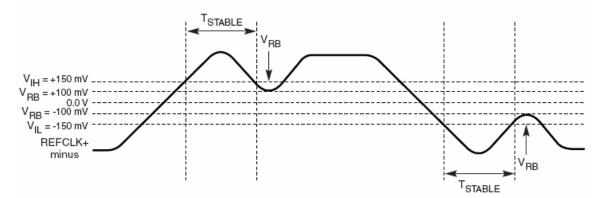

| Ringback                                                                |    |

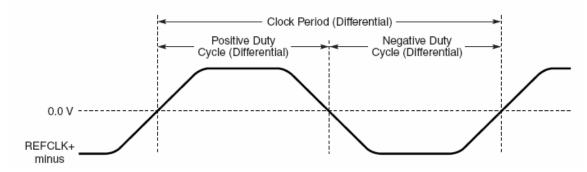

| Period                                                                  |    |

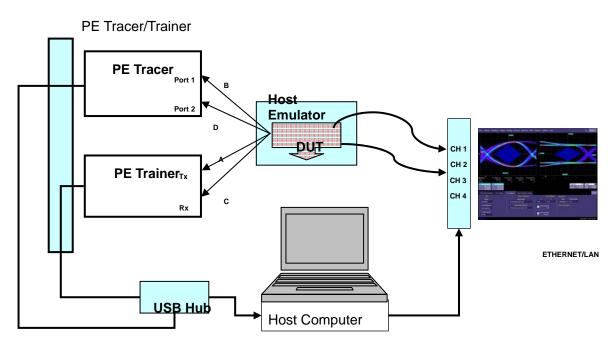

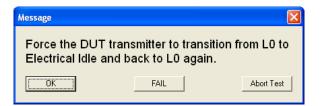

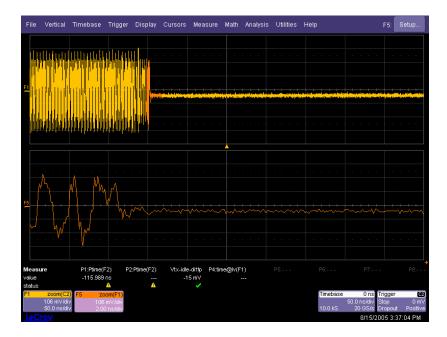

| <b>APPENDIX A – PROTOCOL ANALYZER AND PCI EXPRESS ELECTRICAL TESTS:</b> | 45 |

| Use of Generation Files                                                 |    |

| Block Diagram – System Configuration                                    |    |

| Step sequence for Test 1.7                                              |    |

| Test Steps using X-Replay                                               | 46 |

### **INTRODUCTION TO SDA-PCIE-G2**

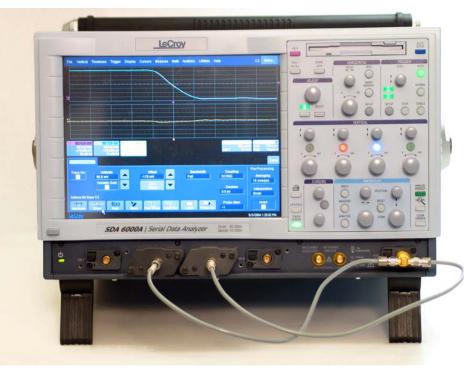

The New LeCroy PCI Express Development Software for the SDA 6000A, SDA 6020 and SDA 11000 serial data analyzers is designed with two major objectives in mind:

- First and foremost, SDA-PCIE-G2 provides the necessary tools to develop PCI Express-compliant devices in a systematic, step-by-step fashion, in accordance with the latest standards and specification documents published by PCI-SIG.

- Quick and easy access to all the compliance test requirements from the base and add-in card specifications, and summarized in the Signal Quality Test ("Sigtest") electrical test tool. LeCroy uses the Intel-certified DLL and integrates the tool into the X-Stream processing software, thus enabling in-process measurement and reporting of PCI Express critical parameters.

The standard features of the SDA also provide a broad tool set for advanced debugging of these interfaces, including jitter, eye pattern, and bit error rate.

The New LeCroy PCI Express Development Software (SDA-PCIE-G2) supersedes the LeCroy PCI Express Compliance software (SDA-PCIE). Existing SDA-PCIE users can upgrade to SDA-PCIE-G2 as an option to the SDA 6000A, SDA 6020 and SDA 11000 Serial Data Analyzers by installing version 4.1.1.3 or later of X-Stream DSO firmware.

### **Required equipment**

- SDA 6000A, SDA 6020 or SDA 11000

- PCI Express Compliance & Development software option (LeCroy SDA-PCIE-G2)

- 2 matched-length SMA cables for single-ended tests

- 2 differential probes (D600-type for SDA 6000A or SDA 6020, D11000PS-type for SDA 11000)

- 1 SMA T connector

- 1 BNC-to-SMA adapter

- 1 compliance test fixture (CLB or CBB as appropriate for testing a system or add-in card)

- A Host computer, though not required, is highly recommended to execute X-Replay, the Compliance & Development Software Engine.

Additionally, SDA-PCIE-G2 takes advantage of LeCroy's full line of PCI Express Protocol tools in order to force the DUT to enter or abandon a particular State for the purpose of making amplitude or timing measurements. These tools are used for SDA-PCIE-G2 implementation. LeCroy recommends the use of the following tools:

- PE Tracer (PCI Express Protocol Analyzer)

- PE Trainer (PCI Express Protocol Exerciser)

- o PE Host Emulator (PCI Express System Board with x8 slot)

For an example featuring the above protocol tools, refer to *Appendix A* section of this manual. Specific instructions on how to use LeCroy's protocol tools can be found at <u>www.lecroy.com</u>

### **PCI Express Compliance Test Fixtures**

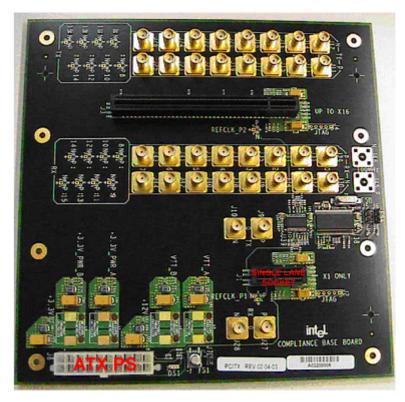

The PCI Express standard describes a set of two fixtures that are used to connect to the signal under test. The fixtures are known as the compliance load board (CLB) and the compliance base board (CBB). The CLB is used to test system boards, and the CBB is used for testing add-in cards. Both the compliance load board and compliance base board are available through the PCI special interest group (PCI-SIG) at <u>www.pci-sig.org</u>

Using SMA type cables, both fixtures allow for the attachment of the positive and negative lines of the differential signals directly to separate channels on the instrument. The 50 ohm impedance on each oscilloscope channel provides the proper loading for compliance testing. All PCI Express add-in cards and system boards must transmit a standard compliance pattern when loaded with 50 ohms to ground on each line, at the same time that no signal is being received. The fixtures are designed to apply the compliance test load to the ports of the device under test. The CBB also has a socket for a standard ATX power supply and a 100 MHz system clock that is used by add-in

### **PCIE-G2 Software Option**

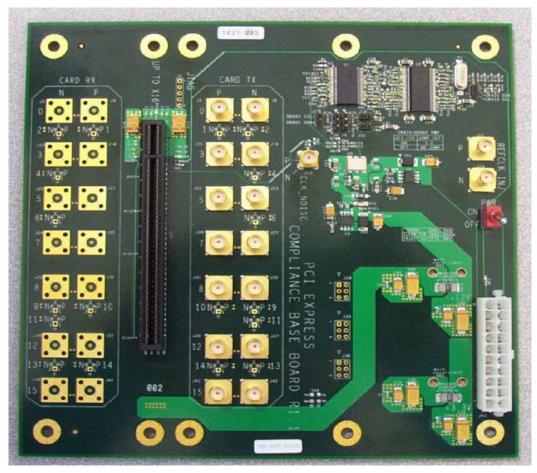

cards plugged into the fixture. Please note that effective May 2005, a CBB compliant with Version 1.1 of PCI Express Base Specification is also available from PCI-SIG. See Figure 3.

Figure 1. Compliance base board (CBB) provides sockets for 1 lane and 16 lane add-in cards. The SMA jacks allow access to the D<sup>+</sup> and D<sup>-</sup> signals from the connectors. The ATX power supply connection is at the bottom edge of the board and the clock is just above the single lane socket.

Figure 2. The compliance load board (CLB) connected to a motherboard. This fixture provides probing access for 1, 4, 8, and 16 lane connectors. This figure shows the 1 lane section being used. The SMA cables connect the D<sup>+</sup> and D<sup>-</sup> signals to the oscilloscope channels.

### PCIE-G2 Software Option

Figure 3. New Compliance base board (CBB) for version 1.1 provides a clean reference clock and clock noise injection capabilities.

### SOFTWARE INSTALLATION AND SYSTEM CONFIGURATION

### What Is X-Replay?

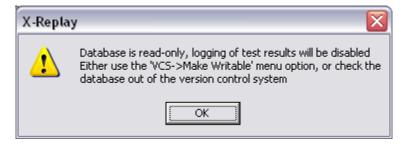

The new PCI Express Software application incorporates X-Replay, a unique application framework. X-Replay is a MS Windows-based application that contains all the commands and instructions necessary to configure, acquire, display, and report measurement results. For instance, X-Replay environment enables you to:

- Create or change test criteria in order to make context-sensitive parametric measurements.

- Export all test results as XML for import into a database program such as Microsoft Access for further manipulation.

- Generate reports from within X-Replay showing the latest test results. Reports are html, i.e., meant to be viewed with Microsoft Internet Explorer.

The PCI Express Compliance software resides in X-Stream DSO software in the scope, and it is activated through the use of an alphanumeric code matched to the scope's serial number. This code is unique to each scope serial number and is activated when ordering SDA-PCIE-G2 software.

While the software key enables the scope to perform the measurements, X-Replay contains the PCI Express script, the test results database and the report generation engine. For ultimate flexibility, X-Replay can be executed from a host computer at a location different from the scope, provided that there is a Windows-compatible network connection.

### **Option Key Installation**

When ordered as an option to a new instrument, no installation is necessary. Installation is required, however, when the option is ordered after the oscilloscope is purchased. An option key will be issued at the time the option is purchased.

To enter the option key code,

- 1. Touch Utilities in the menu bar, then Utilities Setup... in the drop-down menu.

- 2. Select the **Options** tab from the Utilities dialog.

- 3. In the **Options** dialog, touch the **Add Key** button and enter the option key in the dialog box using the onscreen keyboard.

Figure 4. Entering the option key code for the SDA-PCIE-G2 software option

### **CD-ROM** Installation

When ordered as an upgrade to an existing SDA-PCIE option, an Application Software CD-ROM is supplied containing X-Replay and other software installation files. Follow the specific instructions in the Installer application. The installation process will prompt you, as required, for specific location of data files and test results, reports, scripts, etc.

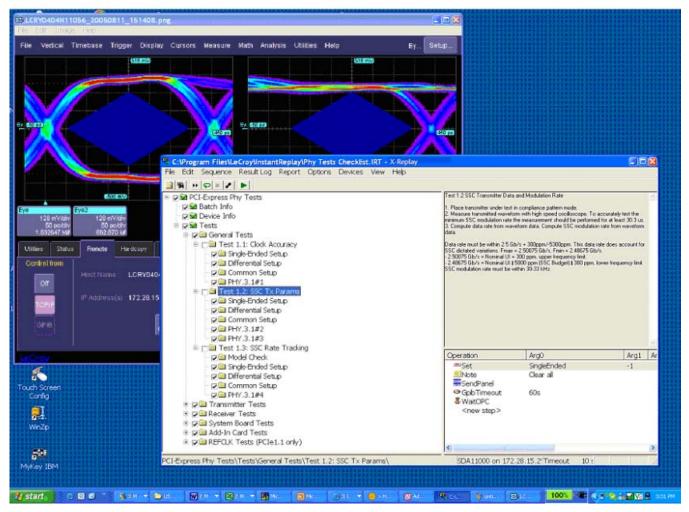

### Typical (Recommended) Configuration

SDA-PCIE-G2 software can be executed from the scope PC or from a Host PC. By default, a new scope will come equipped with X-Replay installed in the scope. LeCroy recommends that you run SDA-PCIE-G2 in a scope equipped with Dual Monitor Display capability (option DMD-1), such that the waveform and measurements are displayed on the scope LCD display, whereas the X-Replay application and test results are displayed on a second

monitor. By default, the scope appears as a local host (IP address is 127.0.0.1) when X-Replay is running in the scope computer. To verify its correct operation, the following steps must be taken once the scope is turned on:

- 1. Minimize the X-Stream DSO window.

- 2. Run X-Replay.

- 3. Select **Scope Manager**. The scope selector window should display the scope attached (in this case, an SDA 11000)

- 4. Press the Test button. A message box will indicate that the test is OK. X-Replay is now ready for use.

| 📢 D      | :Wppl         | ications\PC                                    | I-Express\ | Phy Tests                    | Checklist. IR      | Τ-                                                                                                                                                                                                                                   |                                    |                                                                                   |                  | - <b>-</b> ×                         |

|----------|---------------|------------------------------------------------|------------|------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------|------------------|--------------------------------------|

| File     | Edit S        | equence Gro                                    | oup Learn  | Test Step                    | Result Log Re      | port Options Devices                                                                                                                                                                                                                 | View Help                          |                                                                                   |                  |                                      |

| 3        | <b>1</b>      | +   <b>\$</b>   =   •                          |            | <u> </u>                     | Ballin Cond        | 🛯 🤷 🐯 🗷 🖢                                                                                                                                                                                                                            | Del                                |                                                                                   |                  |                                      |

|          | ÷             |                                                |            | lock Accuracy<br>Ended Setup |                    |                                                                                                                                                                                                                                      |                                    |                                                                                   |                  | 2                                    |

| -        | Sco           | ope Selecto                                    | г          |                              |                    |                                                                                                                                                                                                                                      |                                    |                                                                                   | ?                | 2 Ar                                 |

| 1        |               | Device                                         | Status     | Bus                          | Address            | Soft Rev                                                                                                                                                                                                                             | S/N                                |                                                                                   | ОК               |                                      |

| 661<br>X | 8             | SDA11000                                       | Alive      | Net                          | 127.0.0.1          | 0.0.0 (build 73064)                                                                                                                                                                                                                  | LCRY0404N1                         | 1056                                                                              | Cancel           |                                      |

|          |               |                                                |            | 1                            |                    |                                                                                                                                                                                                                                      |                                    | 1                                                                                 |                  |                                      |

|          |               |                                                | Remove     | Enable                       |                    | Tes                                                                                                                                                                                                                                  |                                    |                                                                                   |                  | >                                    |

|          |               | or Name<br>Steven.Sa<br>Steven.Sa<br>Steven.Sa | LCRY0404N1 | 1056 10:1                    | 33.0 °⊂<br>33.0 °⊂ | Innescamp         Ct           ≤         2005/08/0         Se           ≤         2005/08/0         Se            2005/08/0         Al            2005/08/0         F            2005/08/0         F            2005/08/0         Te | endVbsQuery<br>portTest<br>ndScope | Explanation<br>keyword 0 numeric c<br>keyword 0 numeric c<br>Total Steps Executed | omparison failed | SDA1<br>SDA1<br>SDA1<br>SDA1<br>SDA1 |

|          |               |                                                |            |                              |                    | <                                                                                                                                                                                                                                    |                                    | 1000                                                                              |                  |                                      |

| -        | Ready<br>star | 6                                              | o 🎗 🏾 🛛    | M LeCroy                     | SDA11000           | SDA1100                                                                                                                                                                                                                              | 0 on 127.0.0.1<br>hs\PCI-E         | Timeout                                                                           | 10 s             | $\mathbf{M}$                         |

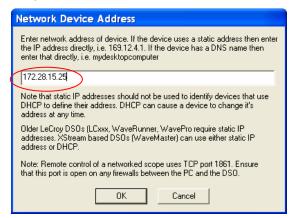

### Remote (Networked) Configuration

Of course, it is also possible to run SDA-PCIE-G2 by installing X-Replay in a host PC, controlling the scope through a Windows Network / LAN Connection. This may allow you to run other instruments or applications from the host PC, for example setting up and configuring the LeCroy PE Protocol and Host Emulator instruments. The scope must already be configured and an IP address (fixed or network-assigned) must already be established.

Follow these example steps to set up the scope using X-Replay over a LAN:

1. In the scope, verify in the **Utilities** → **Remote** dialog that the scope has an IP address, control is set to TCP/IP as shown below:

| Utilities | Status | Remote | Hardcopy                  | Aux Output         | Date/Time | Options |                                                            | Close                                                    |

|-----------|--------|--------|---------------------------|--------------------|-----------|---------|------------------------------------------------------------|----------------------------------------------------------|

| Control   | from   |        |                           | TCP/IP             |           |         | Security                                                   | Remote Control Assistant                                 |

| Оff       |        |        | : LCRY04<br>(s): 172.28.1 | 04N11056<br>5.25   |           |         | Restrict remote control<br>to specified clients?<br>No Yes | Show Remote<br>Control Log<br>Log Mode                   |

| GPIE      |        |        |                           | Net<br>Connections |           |         |                                                            | Errors Only<br>Reset to Errors Only and clear at startup |

- 2. Make sure that the host PC is connected to the same LAN as the scope. If unsure, contact your system administrator.

- 3. Run X-Replay in the host PC and select the **Devices** menu, then **Scope Selector**. The screen will show no devices enabled at this time. Click the **Add** button:

| 2 | icope Selecto | r      |        |         |          |      |           |                | ? 🛛    |

|---|---------------|--------|--------|---------|----------|------|-----------|----------------|--------|

|   | Device        | Status | Bus    | Address | Soft Rev | S/N  |           |                | ОК     |

|   |               |        |        |         |          |      |           |                | Cancel |

|   |               |        |        |         |          |      |           |                |        |

|   |               |        |        |         |          |      |           |                |        |

|   |               |        |        |         |          |      |           |                |        |

|   |               |        |        |         |          |      |           |                |        |

| ( | Add           | move   | Enable |         |          | Test | Propertie | s Use Selected |        |

4. Select **Network** as the connection method:

| A | dd Device              | ×                          |

|---|------------------------|----------------------------|

|   | How is the scope conne | cted to the PC?            |

|   | GPIB                   | GPIB (IEEE 488) connection |

| < | Network                | CP/IP connection           |

|   |                        | Cancel                     |

5. Enter the IP address from step #1

6. Click **OK**. The Scope Selector window displays the correct information about the scope connected to the LAN. In our example, an SDA 11000 is connected, as shown below:

| s | cope Selecto | r               |            |                      |                      |                       |           |                | ? 🛛          |

|---|--------------|-----------------|------------|----------------------|----------------------|-----------------------|-----------|----------------|--------------|

|   | Device       | Status<br>Alive | Bus<br>Net | Address 172.28.15.25 | Soft Rev<br>0.0.0 (b | S/N<br>LCRY0404N11058 | 6         |                | OK<br>Cancel |

|   | Add Re       | move            | Enable     |                      |                      | Test                  | Propertie | s Use Selected |              |

### INTRODUCTION TO PCI-EXPRESS

PCI Express is a serial version of the commonly used PCI bus designed for PC's and servers. This serial interface adds scalability through the use of multiple lanes, and flexibility through such features as switching. PCI Express is a multi-lane interface that operates at a signaling rate of 2.5 Gb/s on each lane. The differential signal contains both normal and inverted signal lines designated D<sup>+</sup> and D<sup>-</sup>, and the signaling voltages are nominally 800 mV peak-to-peak.

PCI Express is designed to operate on standard PC motherboards using low-cost PCI-type sockets. This implies several things about the signal characteristics. First, spread spectrum clocking must be supported to control emissions in desktop applications. Second, because standard PC motherboards must be used, the signal is preemphasized to control inter-symbol interference. Finally, many implementations of serial data receivers employ an "over sampling" mode that takes many samples per bit to find the data transitions rather than using a recovered clock for this purpose.

### **PCI Express Device Development Process**

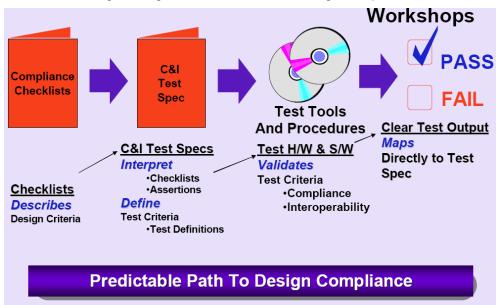

With the introduction of PCI Express Gen2 in Spring 2005, High Speed PCI Express has arrived. As a result, PCI Express standards are quickly evolving to allow existing Gen 1 (2.5 Gb/sec) designs to interact with the new, demanding 5 Gb/sec requirements. New requirements for PCI Express Gen1 are now identified in the new PCIE Version 1.1 specification, effective April 2005. PCI-SIG encourages new and experienced electrical interface designers to undertake new designs using a "Predictable Path to Design Compliance."

### **PCI Express Device Development Process and Compliance Tests**

The PCI Express **Compliance** test requirements are derived from the test specification document, which is interpreted from the design checklist. The design checklist is a set of requirements that must all be met during the design phase of a PCI Express-compliant device. An example of a few requirements from the design checklist is shown below:

| PHY.2.6#1  | Training sequence ordered-sets are never scrambled but always 8b/10b encoded. | yes<br>no |

|------------|-------------------------------------------------------------------------------|-----------|

| PHY.3.1#25 | The receiver terminations must remain enabled in Electrical Idle.             | yes<br>no |

| PHY.3.2#5  | The Beacon signal must contain minimum width pulses >= 2 ns.                  | yes<br>no |

Figure 5. Example requirements from the PCI Express design checklist

The test specification / Electrical Design Considerations contains a list of **Assertions** that are derived from the checklist. For example, the symbol rate must be 2.5 Gb/s +/-300 ppm. Each assertion has a specific measurement that is used to verify it, the **Test Number**. While there are many tests in the specification, only the signal quality test is performed for **Compliance**.

The new LeCroy PCI Express software supports the measurement of PCI Express signals in two modes of operation:

- **Compliance Test Mode**, or signal quality test, based on Intel's sigtest dynamically linked library (dll) and used for test and evaluation at PCI-SIG sponsored electrical test workshops. These tests are covered in the Electrical Design Considerations document under Tests 1.4 and 1.5, and can be accessed by manual control on the DSO or by selecting the corresponding tests under X-Replay.

- **Checklist Test Mode, or Designers Checklist Mode**. In this case, the X-Replay script provides capabilities to run all the test steps required or some group of tests, as many times as specified, and in accordance with the form factor (Add-In card, System card) supported by the device under development. For example, a developer may only be interested in the Tx performance of the chipset, then only the Transmitter Tests are selected for verification.

### PCI EXPRESS MEASUREMENT THEORY

### **Eye Pattern and Jitter Measurements**

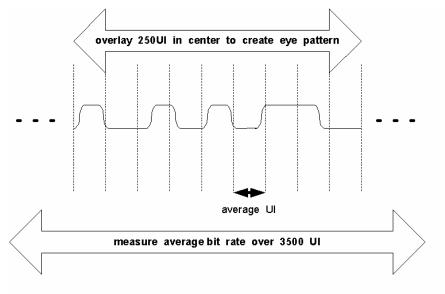

PCI Express signal quality tests are performed using eye pattern analysis. The eye pattern allows measurement of voltage and jitter. The measurement methodology that has been adopted for eye patterns in this standard is designed to accommodate the requirements of over-sampling detectors and spread spectrum clocking. The method relies on the acquisition of consecutive unit intervals of the data stream sampled at a minimum rate of 20 GS/s.

### Version 1.0a Measurements

The average symbol period is measured over 3500 unit intervals (UI). This value is then used to create an eye pattern over a segment of 250 unit intervals in the center of the 3500 UI window. The eye pattern is generated by dividing the 250 UI segment into equal-length segments set by the measured average symbol period. The 250 UI segment is chosen to encompass the range in which over-sampling detectors are affected by jitter. The 3500 UI window is chosen to provide the most accurate symbol period measurement while being minimally affected by any spread spectrum clock that may be on the signal.

# Figure 6. Compliance eye pattern creation (version 1.0a). The eye pattern is created by dividing the center 250 UI of the waveform into segments that are the width of the average UI measured over 3500 unit intervals.

The eye pattern is produced by dividing the 250 UI segment into segments that are 1 nominal UI long. The nominal UI for a given 250 UI segment is measured by finding the median value over a 3500 UI segment whose center 250 UI contain the measurement window. The 1 UI segments are overlain by lining up the median UI boundaries. The median UI was chosen in the standard rather than the average because the median value is more accurate in the presence of low-frequency jitter, such as that caused by spread spectrum clocking.

### Version 1.1 Measurements

The revised version of the specification places a premium on the acquisition record size requirements: 1 million UI, which translates to 8 Mpts acquisition record size when running at 20 GS/s. The reference clock is assumed to have been cleaned, i.e., contributes zero jitter:

"The TTX-EYE-MEDIAN-to-MAX-JITTER specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total TX jitter budget using the clock recovery function specified in Section 4.3.3.2 of the PCI Express Base Specification. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is

approximately equal, as opposed to the averaged time value. This parameter is measured with the equivalent of a zero-jitter reference clock. The TTX-EYE measurement is to be met at the target bit error rate. The TTX-EYE-MEDIAN-to-MAX-JITTER is to be met using the compliance pattern at a sample size of 1,000,000 UI." The new clock recovery applies a first order high-pass filter with a -3 dB cutoff frequency of 1.5 MHz, rolling off at -20 dB/decade.

In addition, the new clock recovery function will apply to devices (for example, Add-in cards) that rely on a clean clock. For System board designers, however, the burden of proving that the reference clock is a clean clock is a NEW requirement for PCIE Version 1.1 compliant designs.

### PREPARING TO MAKE PCI EXPRESS MEASUREMENTS

### **Channel Deskew (SMA Cables)**

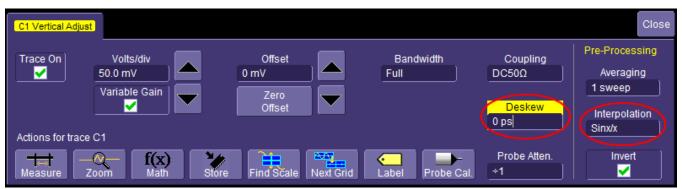

PCI Express signals are properly probed using two separate channels on the oscilloscope connected to the appropriate SMA jacks on the test fixture. The highest measurement accuracy is achieved when the timing skew between the two channels is calibrated. This is performed using the "Deskew" control on one of the two channels to which the differential signal is connected, as follows:

1. Attach the calibrator signal to both input channels using a T connector to rout the calibrator signal on the SDA front panel through the same cables that will be connected to the fixture.

Figure 7. Deskew cable setup. The calibrator signal is connected to the cables using a T connector or resistive divider. The calibrator peak voltage should be set to the same value as the nominal voltage of  $D^{*}$  and D.

- 2. Set interpolation of both channels to Sin(x)/x, using the Interpolation control in the Vertical Adjust dialog for each channel.

- 3. Check the Invert checkbox on one channel.

Figure 8. Deskew control in channel menu. Adjust this value to achieve minimum skew.

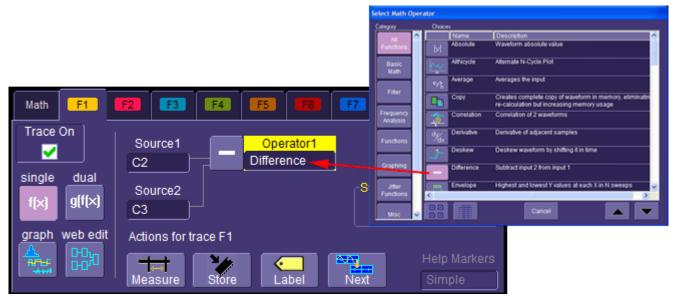

4. Create a Difference math waveform by selecting Math in the menu bar, then Math Setup... in the dropdown menu. Touch the "Operator1" field and select Difference from the Select Math Operator menu. Enter the channels to which your signal is connected in the Source1 and Source2 fields. The math function is thus defined as the difference between the 2 channels probing the D<sup>+</sup> and D<sup>-</sup> signals.

### Figure 9. Math setup

5. While viewing the math trace, adjust the **Deskew** control in one of the channels until the math trace is as flat as possible.

Note: With the Deskew control highlighted, you can use the front panel adjust knob to make the adjustment.

The best accuracy is achieved by setting the level of the calibrator signal to match the expected levels of the signal under test, and with the calibrator set to its maximum frequency (5 MHz). The calibrator settings can be found in **Utilities**  $\rightarrow$  **Aux Output**.

### **Differential Probe Calibration**

The PCI Express signal can be applied to a single channel of the SDA using a differential probe, or directly to two channels using one of the test fixtures described above. In either case, the signal level should be maximized on the instrument to achieve the best overall accuracy. The signal level is set in the **Vertical Adjust** dialog, or by using the front panel knobs. The best peaking can be achieved by checking the **Variable Gain** checkbox, which allows finer gain steps in the control knobs.

With the introduction of the 40 GS/s, 2 channel, 11 GHz BW (20 GS/s, 4 channel, 6 GHz) scope with Digital Bandwidth Interleaving (DBI), high-speed PCI Express Gen 2 measurements can now be accomplished. Additionally, the use of two D11000 probes enables the measurement of inter-lane skew on the DBI-enabled channels.

Figure 10. Signals properly adjusted for best accuracy. The signal levels should be adjusted in the "Vertical Adjust" dialog so that at least 6 vertical divisions are filled.

### For SDA 6000A

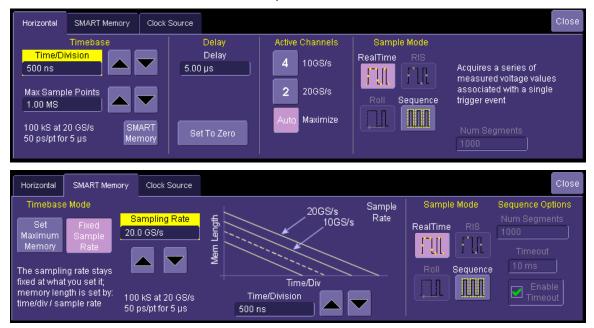

The horizontal scale should be set to a fixed sampling rate of 20 GS/s. This requires that **Auto** or **2** channels be selected in the **Active Channels** control in the **Horizontal** (Timebase) dialog. The record length should be set to a minimum of 8 MS using the **Time/Division** control or the front panel horizontal scale knob. Longer records give more accurate results but also take more time to compute.

Figure 11. Horizontal and memory setup menus properly configured for testing PCI Express signals. The maximum (20 GS/s) sampling rate must be used. The SDA6020 model does not have the "Active Channels" control since all channels sample at 20 GS/s.

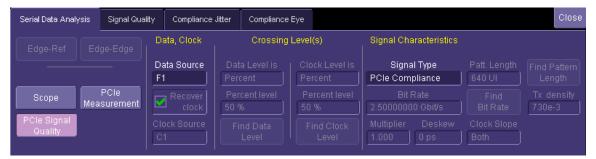

The signal under test is selected from the **Data Source** menu in the **Serial Data Analysis** main dialog. The source can be any channel, memory, or math trace. If a differential probe is being used to couple the signal to the instrument, the channel to which the probe is attached should be entered into the **Data Source** control. When probing with 2 channels of the instrument attached to a compliance test fixture, a math trace should be defined as the difference between the channel connected to the D<sup>+</sup> and the channel connected to the D<sup>-</sup> lines on the fixture. The channels should be deskewed as described above.

It is also possible to perform measurements on waveform files stored in memory. either on the system hard disk or in non-volatile memory. Subtract the memory traces if they are stored as separate (+ and -) waveforms, as described above, or enter the memory into the **Data Source** control directly.

| Serial Data Analysis   | Signal Qua       | lity               |                          |                           |                                 |                      | Close              |

|------------------------|------------------|--------------------|--------------------------|---------------------------|---------------------------------|----------------------|--------------------|

| Edge-Ref Ed            |                  | Data, Clock        | Crossing                 | Level(s)                  | Signal Characteristics          |                      |                    |

|                        |                  | Data Source<br>M2  | Data Level is<br>Percent | Clock Level is<br>Percent | Signal Type<br>PCIe Compliance  | Patt. Length<br>2 UI |                    |

|                        | PCIe<br>surement | Recover<br>clock   | Percent level 50 %       | Percent level<br>50 %     | Bit Rate<br>2.50000000 Gbit/s   |                      | Tx density<br>1.00 |

| PCIe Signal<br>Quality |                  | Clock Source<br>C1 |                          |                           | Multiplier Deskew<br>1.000 0 ps | Clock Slope<br>Both  |                    |

### COMPLIANCE TEST MODE

This section describes how to execute the "PCIe Compliance" test built into the SDA, from the SDA's user interface. Information about using X-Replay to automatically run tests is in the section titled "Checklist Test", below.

To select the compliance test mode, from Serial Data Analysis menu select "PCIe Compliance" for Signal Type. The following menu appears:

### Performing a Compliance Test – PCle Signal Quality

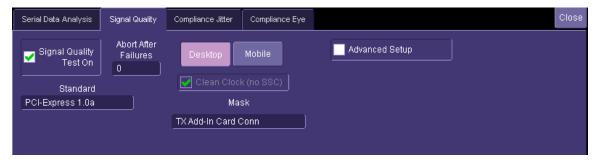

Compliance testing is defined by the PCI-SIG (PCI Special Interest Group) as consisting of a pair of eye pattern template tests and a set of jitter measurements derived from the eye pattern zero crossings. Compliance testing also includes measurement of the bit (data) rate, bit period (or UI), and voltage levels. Select the **Signal Quality** tab; the following dialog is now displayed:

A compliance measurement is started when the **Signal Quality Test On** checkbox is checked. The compliance test will start and messages indicating the start and completion of the test will be displayed on the bottom left edge of the instrument display. Two eye patterns are displayed in the upper half of the display when the test is complete. The one on the left shows the waveform for transition sections of the trace, while the one on the right shows the non-transition eyes (see the figure below).

First, the form factor (Desktop or Mobile) button is chosen:

-STREAM

Figure 12. Add-In Card Test

The **Standard** control allows you to select PCI-Express v1.0a, PCI-Express v1.1, or PCI Express v2.0 (SDA 11000 only) as the signal under test. The **Abort After Failures** control will terminate the acquisition after the number of mask violations specified in this field. Whenever **Add-In card Masks** are selected, the **Clean Clock** checkbox is checked by default. For Tx or Rx package pin tests, however, selection of a clean clock is optional. Finally, for System Board tests the clean reference clock is not permitted. The PCI Express application running under X-Replay contains extensive reference clock test routines to characterize the existence of a clean clock.

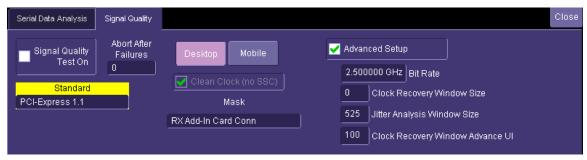

The **Advanced Setup** checkbox allows the individual adjustment of jitter and clock recovery window settings used in the creation of eye diagrams. These are different depending on the revision level of the PCI Express specification selected. For example, for PCI Express v1.1 add-in card, the following values are used:

Figure 13. PCI Express Add-In Card Mask Settings (Tested with a Clean Clock)

The "**Compliance Jitter**" and "**Compliance Eye**" tabs display tables of jitter, timing, and voltage measurements. Each measurement has a checkbox to its left indicating pass or fail. A green check in this box indicates that the

### **PCIE-G2 Software Option**

corresponding parameter meets the compliance specification. A failure is indicated by a blank box adjacent to the parameter.

| Serial Data Analysis                                        | Signal Quality                                                     | Compliance Jitte | er Compliance                                                                | Eye |                                                                             |                                                                  | Close                                                                                           |

|-------------------------------------------------------------|--------------------------------------------------------------------|------------------|------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Mask violations<br>Worst total<br>Pass<br>1245<br>Fail<br>O | Unit Interva<br>mea<br>400.067<br>Max<br>400.067<br>Min<br>400.067 | n<br>7 ps 🖌      | ian Peak Jitter<br>mean<br>29.195 ps<br>Max<br>55.447 ps<br>Min<br>18.831 ps |     | o Peak Jitter<br>mean<br>52.281 ps<br>Max<br>101.934 ps<br>Min<br>34.910 ps | Per Edge<br>RMS Jitter<br>11.766 ps<br>Total Edges<br>479.723e+3 | Data Rate<br>2.499581 Gbit/s<br>Min Crossover Time<br>378.254 ps<br>Min Eye Width<br>298.133 ps |

### For the Compliance Eye:

| Serial Data Analysis | Signal Quality | Compliance Jitter           | Co | ompliance Eye                           |                      | Clos             |

|----------------------|----------------|-----------------------------|----|-----------------------------------------|----------------------|------------------|

|                      | Transition Eye |                             |    | Non Trans                               | ition Eye            |                  |

| Min Voltag           |                | 1in Bottom Margin<br>123 mV |    | Min Voltage           J         -393 mV | Min Bottom Margin    | Create<br>Report |

| Max Voltag           |                | Min Top Margin<br>33 mV     |    | Max Voltage 402 mV                      | Min Top Margin 97 mV |                  |

| Number Viola         | itions<br>)    |                             |    | Number Violations                       |                      |                  |

The eye patterns and test results can also be exported to HTML using the Create Report button.

It is important to note that Compliance Testing, as defined by PCI-SIG, is a small subset of the electrical checklist considerations document. The X-Replay script (and report) covers many more tests.

### Parameter List – Transmitter Compliance Tests (measured at the Tx package pins)

| Test     | Assertion  | Parameter                     |

|----------|------------|-------------------------------|

| Test 1.5 | PHY.3.2#1  | MaskViolationsTXNonTransition |

| Test 1.5 | PHY.3.2#1  | VtxMaxNonTransition           |

| Test 1.5 | PHY.3.2#1  | VtxMinNonTransition           |

| Test 1.5 | PHY.3.2#14 | VtxMobileMax                  |

| Test 1.5 | PHY.3.2#14 | VtxMobileMax                  |

| Test 1.5 | PHY.3.2#14 | VtxMobileMin                  |

| Test 1.5 | PHY.3.2#14 | VtxMobileMin                  |

| Test 1.5 | PHY.3.2#14 | MaskViolationsTXMobile        |

| Test 1.5 | PHY.3.2#14 | MaskViolationsTXMobile        |

| Test 1.5 | PHY.3.2#14 | MaskViolationsTXMobile        |

| Test 1.5 | PHY.3.2#2  | Vtx-diffp-p                   |

| Test 1.5 | PHY.3.2#2  | VtxMaxTransition              |

| Test 1.5 | PHY.3.2#2  | VtxMinTransition              |

| Test 1.5 | PHY.3.2#2  | MaskViolationsTXTransition    |

| Test 1.5 | PHY.3.3#1  | MaskViolationsTXTotal         |

| Test 1.5 | PHY.3.3#2  | MaxUI                         |

| Test 1.5 | PHY.3.3#2 | AvgUI                   |

|----------|-----------|-------------------------|

| Test 1.5 | PHY.3.3#2 | MinUI                   |

| Test 1.5 | PHY.3.3#4 | TtxEyeMedianToMaxJitter |

| Test 1.4 | PHY.3.3#4 | TtxEyeMedianToMaxJitter |

| Test 1.4 | PHY.3.3#4 | TtxEyeMedianToMaxJitter |

| Test 1.4 | PHY.3.3#9 | TtxEye                  |

#### Parameter List – Add-In Card Compliance Tests (measured at the connector)

| Test     | Assertion | Parameter                        |

|----------|-----------|----------------------------------|

| Test 1.5 | EM.4#19   | VtxaMax                          |

| Test 1.5 | EM.4#19   | MaskViolationsAddInNonTransition |

| Test 1.5 | EM.4#19   | Vtxa_dMin                        |

| Test 1.5 | EM.4#19   | VtxaMin                          |

| Test 1.5 | EM.4#19   | Vtxa_dMax                        |

| Test 1.5 | EM.4#19   | MaskViolationsAddInTransition    |

| Test 1.5 | EM.4#19   | JtxaMedianToMaxJitter            |

| Test 1.5 | EM.4#19   | Ttxa                             |

### Parameter List – System Board Compliance Tests (measured at the connector)

| Test     | Assertion | Parameter                      |

|----------|-----------|--------------------------------|

| Test 1.5 | EM.4#20   | VtxsMax                        |

| Test 1.5 | EM.4#20   | VtxsMin                        |

| Test 1.5 | EM.4#20   | MaskViolationsSysTransition    |

| Test 1.5 | EM.4#20   | Ttxs                           |

| Test 1.5 | EM.4#20   | JtxsMedianToMaxJitter          |

| Test 1.5 | EM.4#20   | Vtxs_dMax                      |

| Test 1.5 | EM.4#20   | Vtxs_dMin                      |

| Test 1.5 | EM.4#20   | MaskViolationsSysNonTransition |

### **Performing a PCI Express Simple Measurement**

A second button is provided in the interface that accesses a set of additional measurements that are part of the PCI Express Base specification but not strictly required in Compliance mode. These measurements are selected by clicking or touching the **PCIe Measurement** button in the SDA main menu. The PCI Express Measurement mode contains a dialog with a measurement selection control. Some measurements such as common mode voltage require separate connections for the D<sup>+</sup> and D<sup>-</sup> signals; two controls for the input sources are provided for these measurements. Measurements are performed by selecting the input sources and selecting the desired measurement from the control.

**Note:** Only measurements that require separate connections for the D<sup>+</sup> and D<sup>-</sup> signals use the channels selected in the PCIe measurements menu. All other measurements use the waveform selected in the "Data Source" control in the SDA main menu.

### **PCIE-G2 Software Option**

| File     | Vertical               | Timeba                | se Trigger               | Display     | Cursors              | Measure       | Math             | Analysis       | Utilities | Help |                 | M2:                      | Setup              |

|----------|------------------------|-----------------------|--------------------------|-------------|----------------------|---------------|------------------|----------------|-----------|------|-----------------|--------------------------|--------------------|

|          |                        |                       |                          |             |                      |               | ( <u>241 m</u> ) | I              |           |      |                 |                          |                    |

| M1 (-100 | us)                    |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          | ( <u>100 µs</u> )  |

|          |                        |                       |                          |             |                      | (-241 m       |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               | (241 m)          | 0              |           |      |                 |                          |                    |

| M2 (-100 | us)                    |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          | ( <u>100 µs</u> )  |

|          |                        |                       |                          |             |                      | (-241 m       | V                |                |           |      |                 |                          |                    |

| Measu    | ıre                    | P1:TxCm/I             | 41,M2) P2:vo             | liff(M1.M2) | P3:VTxD              | e(F2)         | ▲<br>P4:         | _              | P5:       | P6:- |                 | P7:                      | P8:                |

| value    |                        |                       | 90 µV                    | 896 mV      |                      | 30 dB         |                  |                |           |      |                 |                          |                    |

| status   |                        |                       | ×                        | ×           |                      | ×             |                  |                |           |      |                 |                          |                    |

| Pass/F   |                        | Q1:True<br>P1 < 100 m | Q2:Tru<br>V P2≈1         |             | Q3:True<br>P3 ≈ 2 dB | Q4:<br>P8 < 0 |                  | Q.5:<br>P8 < 0 | Q6.<br>P8 |      | Q7:<br>P8 < 0   | Q8:<br>P8 <              |                    |

| (Q1&)    | Q2 & Q3) =             |                       | v P≥∼i<br>Passed         | * '<br>1 Of |                      |               |                  |                |           |      |                 |                          |                    |

| M1       |                        | M2                    |                          |             |                      |               |                  |                |           | Time |                 | 00 µs Trigge             |                    |

|          | 60 mV/di<br>20.0 µs/di |                       | 60 mV/div<br>20.0 µs/div |             |                      |               |                  |                |           | 400  | 2.00 µ<br>kS 20 | us/div Stop<br>GS/s Edge | 0.0 mV<br>Positive |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

| Seria    | al Data Ana            | lysis M               | easure                   |             |                      |               |                  |                |           |      |                 |                          | Close              |

| Me       | asuremen               | nt                    | Sources                  | Cross       | ing levels           |               |                  |                |           |      |                 |                          |                    |

|          | Туре                   |                       | D+                       |             |                      |               |                  |                |           |      |                 |                          |                    |

| Volt     | lage                   |                       | A1 ]                     |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       | D-                       |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       | 12                       |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

|          |                        |                       |                          |             |                      |               |                  |                |           |      |                 |                          |                    |

| LeC      |                        |                       |                          |             |                      |               |                  |                |           |      |                 | 5/3/2004 12              | 2:15:03 PM         |

Figure 14. PCI Express voltage measurements. Note the measurements displayed in parameters P1 and P2 use the signals in sources D<sup>+</sup> and D<sup>-</sup> (M1 and M2 in this case). The de-emphasis measurement (P3) uses the difference waveform between the D<sup>+</sup> and D<sup>-</sup> (defined here in math function F2) and selected in the "Data Source" control in the SDA menu.

### Voltage measurements

- Select the input sources for the measurements. Enter the channels connected to the D<sup>+</sup> and D<sup>-</sup> signals in the appropriate controls.

- 2. Select Voltage in the "Measurement" control.

- 3. The voltage measurements will appear below the grid area on the instrument as follows:

**Note:** The value of the differential peak-to-peak output voltage (P2) is tested against the required value at the transmitter device package pins. The measured value at the CBB or CLB will be lower and could indicate a failure in Q2. The compliance requirements are set by the eye patterns.

| Parameter Number | Measurement                              | Explanation                                                                                                                                                       |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1               | Transmitter DC common mode voltage       | The average value of the waveform formed by adding the D <sup>+</sup> and D <sup>-</sup> signals (V <sub>CMDC</sub> = mean((D <sup>+</sup> + D <sup>-</sup> )/2)) |

| P2               | Differential peak to peak output voltage | Measured as the p-p value of $2^{+} D^{+} - D^{-} $                                                                                                               |

| P3               | Transmitter de-emphasis ratio            | The log of the ratio of the p-p<br>voltage for a transition bit to<br>the p-p voltage of a non-<br>transition bit computed as<br>$20*\log_{10}(V_t/V_{nt})$       |

### Timing measurements

- 1. Select the input sources for the measurements. Enter the channels connected to the D<sup>+</sup> and D<sup>-</sup> signals in the appropriate controls.

- 2. Select **Timing** in the "Measurement" control.

- 3. The timing measurements will appear below the grid area on the instrument as follows:

**Note:** The value of the differential peak-to-peak output voltage (P2) is tested against the required value at the transmitter device package pins. The measured value at the CBB or CLB will be lower and could indicate a failure in Q2. The compliance requirements are set by the eye patterns.

| Parameter Number | Measurement                 | Explanation                                                                                                                        |

|------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| P1               | Tx Rise Time D⁺             | Transition time, from 20% to<br>80% for all rising edges in the<br>acquisition, as a fraction of a<br>UI (1 UI= 400 ps for Gen 1)  |

| P2               | Tx Fall Time D⁺             | Transition time, from 80% to<br>20% for all falling edges in the<br>acquisition, as a fraction of a<br>UI (1 UI= 400 ps for Gen 1) |

| P3               | Tx Rise Time D <sup>-</sup> | Transition time, from 20% to<br>80% for all rising edges in the<br>acquisition, as a fraction of a<br>UI (1 UI= 400 ps for Gen 1)  |

| P4               | Tx Fall Time D <sup>.</sup> | Transition time, from 80% to<br>20% for all falling edges in the<br>acquisition, as a fraction of a<br>UI (1 UI= 400 ps for Gen 1) |

### SSC measurements

- Select the input sources for the measurements. Enter the channels connected to the source and destination signals in the appropriate controls. They are two directions on same lane. Signals can be input using several probing arrangements:

- a) two single ended probes seeing half of each signal, or

- b) two diff probes (for SDA 6000A, these probes should be in channels 2 and 3),

- c) 4 single-ended SMA probes the sources are two math functions that subtract the input pairs (SDA 6020)

- 2. Select "SSC" in the [Measurement] control.

- 3. The SSC measurements will appear below the grid area on the instrument as follows:

# PCIE-G2 Software Option

| Parameter Number | Measurement            | Explanation                                                     |

|------------------|------------------------|-----------------------------------------------------------------|

| P1               | SSC Min                | Ratio of minimum to max<br>transfer rate. Pass if > 2.49G<br>UI |

| P2               | SSC Max                | Ratio of minimum to max transfer rate. Pass if < 2.5G UI        |

| P3               | SSC Frequency Signal 1 | Frequency of SSC Track, must be between 30 and 33 kHz           |

| P4               | SSC Min                | Ratio of minimum to max<br>transfer rate. Pass if > 2.49G<br>UI |

| P5               | SSC Max                | Ratio of minimum to max<br>transfer rate. Pass if < 2.5G UI     |

| P6               | SSC Frequency Signal 2 | Frequency of SSC Track, must be between 30 and 33 kHz           |

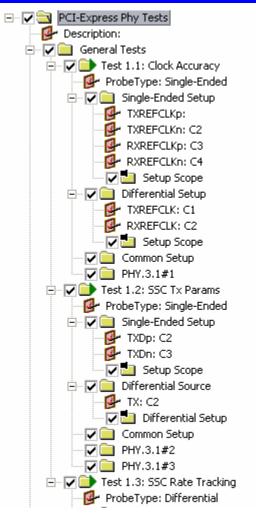

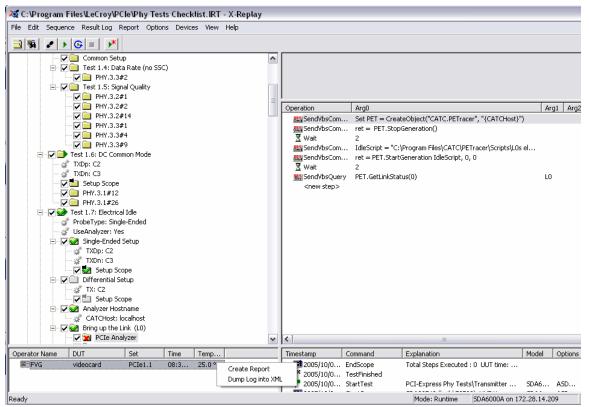

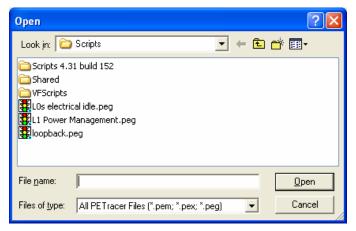

### CHECKLIST TEST MODE OF OPERATION

All the tests covered by this Manual refer to the PHY Electrical Test Considerations Rev 1.0, dated April 26, 2004. This section covers use of X-Replay and the supplied "Phy Tests Checklist.irt" script to perform tests described in the PHY Electrical Test Considerations, and to generate a report from X-Replay using the supplied stylesheet "XReplayPCIE\_Report.xslt"

X-Replay allows you how to test PCI Express functionality in several ways:

- Select, repeat, and skip tests as required to demonstrate or develop different PHY functions.

- Establish Test Limits for each of the versions of the PCI Express specification, and modify create or delete entire test limit sets.

- Generate Test Reports based on the tests actually run.

- Query the database for test results from prior test sessions or experiment runs.

The X-Replay application display is divided into several windows (clockwise, from upper left hand):

- Test Sequence Window

- Test Description Window

- Commands Window

- Activity Log Window

- Session Window

### **Use of Configuration Variables in Test Sequences**

Configuration Variables allow you to define system inputs such as signal sources, probe types, specification parameter set to be used for testing, form factors, and other global conditions. These variables can be set prior to the start of testing, or changed in between test runs.

| ProbeType: Single-Ended                              | Select an entry in the list 🛛 🔀                               |

|------------------------------------------------------|---------------------------------------------------------------|

|                                                      | Scope channel to use for transmitter's D+ for lane under test |

| Vifferential Setup     TXREFCLK: C1     KXREFCLK: C2 | OK                                                            |

Right-clicking on any variable allows you to reset the variable to its default setting or to change the value to be used for subsequent tests.

| 🥸 C:\Program Files\LeCroy\XReplay\Phy Tes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                                                                                                                                                                                                                                                             | play                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                        |                    |                                                                                                                                                                                         |                       |                                                                                                                                                                                | _ 🗆 🗙                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| ile Edit Sequence Result Log Report Options [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Device | is ⊻iew <u>H</u> elp                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                        |                    |                                                                                                                                                                                         |                       |                                                                                                                                                                                |                                                                                                                                                         |